温馨提示:这篇文章已超过472天没有更新,请注意相关的内容是否还可用!

摘要:,,本文介绍了FPGA与SPI总线的基本概念及其在通用接口模块设计中的应用。FPGA作为一种可编程逻辑器件,通过SPI总线实现与其他设备的数据传输。文章详细阐述了SPI总线的工作原理及其在FPGA设计中的作用,同时探讨了通用接口模块的设计方法和实现过程。该设计利用FPGA的高性能并行处理能力,结合SPI总线的通信功能,实现了高效的数据传输和接口控制。

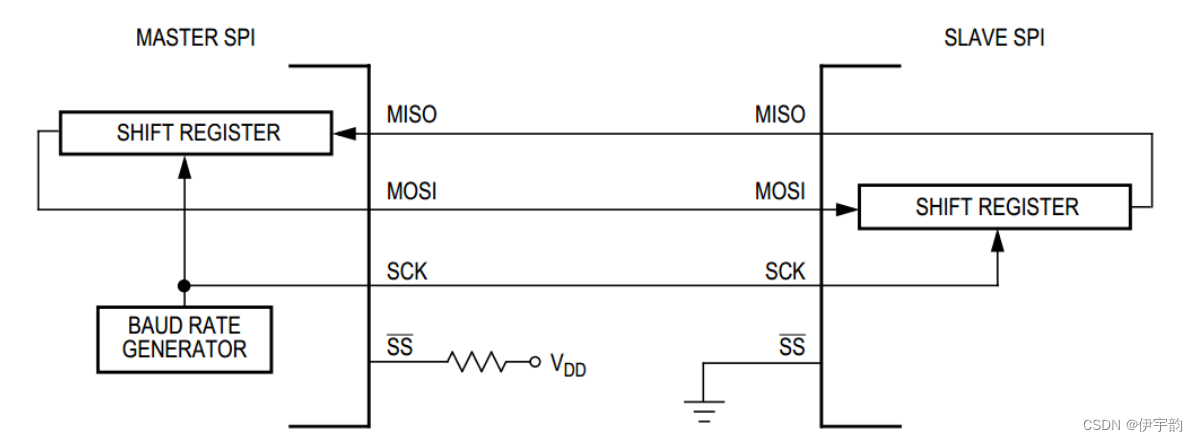

SPI,即串行外设接口(Serial Peripheral Interface)的缩写,是一种高速、全双工、同步的通信总线,用于芯片之间的数据传输,SPI系统通过四根线:串行时钟线(SCK)、主机输入/从机输出数据线(MISO)、主机输出/从机输入数据线(MOSI)和低电平有效的从机选择线(NSS)与各种标准外围器件接口相连。

1、MISO:主设备输入/从设备输出引脚,在从模式下发送数据,在主模式下接收数据。

2、MOSI:主设备输出/从设备输入引脚,在主模式下发送数据,在从模式下接收数据。

3、SCK:串口时钟,作为主设备的输出,从设备的输入。

4、NSS:从设备选择,这是一个可选的引脚,用于选择主/从设备。

SPI是一个环形总线结构,由NSS、SCK、MISO、MOSI构成,数据在主和从设备之间串行地传输(MSB位优先)。

电路连接与硬件拓扑

以下是SPI设备的基本连接示意图,SPI数据传输原理基于主从设备内部移位寄存器的数据交换。

主从设备间数据交换逻辑示意图如下:

硬件拓扑结构包括:

1、单主机单从机

2、单主机多从机(片选方式)

3、菊花链方式

SPI传输模式

通过设置控制寄存器SPICR1中的CPOL(时钟极性)和CPHA(时钟相位),SPI可以分成四种传输模式。

SPI时序图

详细描述了SPI在CPHA=0和CPHA=1两种情况下的时序图。

五、SPI通用接口用户端模块-Verilog代码设计

这部分包括SPI通用接口用户端的设计框图和根据简单分析编写的Verilog代码,设计框图描述了模块的主要组成部分和功能,代码部分实现了SPI通信的基本功能,包括分频计数器的设计、比特计数器和字节计数器的设计、数据发送和接收等,代码中包含了必要的注释,以便于理解,需要注意的是,代码中的某些部分需要根据具体的硬件环境和需求进行调整和优化。

还没有评论,来说两句吧...