温馨提示:这篇文章已超过469天没有更新,请注意相关的内容是否还可用!

摘要:,,关于Xilinx FPGA使用Vivado工具生成bit文件时的约束要点,主要包括:需要熟悉FPGA的特性和资源,以便合理分配硬件资源并设置正确的约束条件;在编程过程中,要遵循正确的流程,包括设计输入、综合、实现和生成bit文件等步骤;生成bit文件时,应注意约束文件的编写,包括时钟、输入输出、内存等参数的设置,以确保生成的bit文件符合设计要求并能在FPGA上正确运行。

在使用Xilinx FPGA进行Vivado设计时,生成bit文件时添加约束是必要的步骤,这些约束涉及设计配置、引脚分配、时钟频率等参数,确保设计正确实现并满足性能要求,通过添加约束,可以优化FPGA资源利用,提高设计效率,确保最终生成的bit文件符合项目需求,在Vivado生成bit文件过程中,合理添加约束是确保FPGA设计成功的关键因素。

配置模式概述

在Vivado设计过程中,生成的bit流文件需要通过特定的配置引脚导入到FPGA中,不同的配置模式决定了不同的配置方式,可选的配置模式包括Master SPI x1/x2/x4、Master Serial、Slave Serial、Master BPI-Up x8/x16、Slave SelectMap x8/x16/x32、JTAG/Boundary Scan以及Master SelectMap x8/16等。

配置数据存储在FPGA的CMOS锁存器中,每次掉电后数据都会丢失,上电之后会重新配置,若选择片外存储器如SPI Flash存储配置数据,并设置相应的配置模式,上电后可自动配置FPGA。

UG470和UG570详细介绍了7系列和UltraScale系列的配置方法,本文主要介绍在Vivado中的设置方法,每种配置模式都有一些相关的接口管脚,这些管脚可能分布在不同的I/O bank中,Bank0中有一些专用管脚用于所有的配置模式;UltraScale的Bank65、7系列的Bank14和Bank15包含了各种配置模式的专用管脚。

纯FPGA和ZYNQ的配置方式

纯FPGA的配置是通过外部FLASH加载的,而ZYNQ的FLASH加载不是通过FPGA,而是通过ARM,某些配置模式如QSPI X1 X4只适用于纯FPGA,ZYNQ一般只配置压缩和电压。

若FPGA选择生成bit文件为QSPI X4的,在批量烧写完FLASH之后再贴装的情况下,需要工厂烧录器设置为x4的烧写模式,否则,贴装之后FPGA可能无法正常工作。

三、如何在Vivado下设置BITSTREAM配置信息

对于纯FPGA情况:

1、打开综合后或实现后的设计。

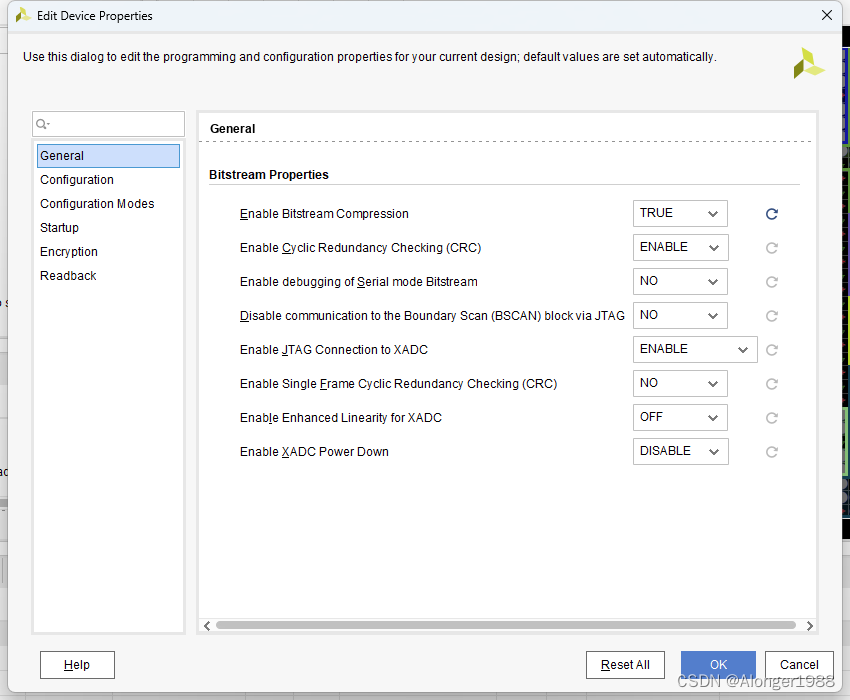

2、依次点击Tools -> Edit Device Properties进入设置界面。

3、选择压缩bit流以提高固化速度。

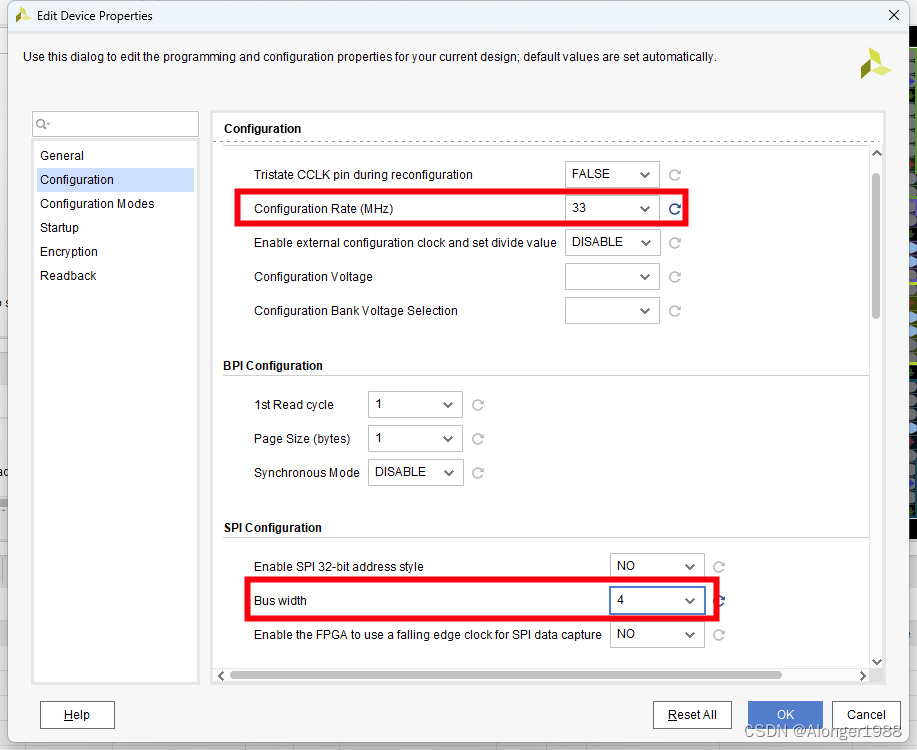

4、选择合适的固化速率,并适当设置高一些。

5、设置SPI的bus width,因为使用的是QSPI,所以这里要设置为4。

6、选择编程模式,因为将程序固化到flash中,以后上电自动从flash读取程序,所以勾选相应的选项,JTAG是一直且默认勾选的。

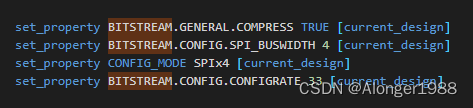

7、在约束文件中插入特定的代码片段来设置CFGBVS、CONFIG_VOLTAGE等相关参数。

对于ZYNQ情况:

如果是ZYNQ的FPGA,由于ZYNQ的FLASH加载是通过ARM进行的,所以设置相对简单,只需在Edit Device Properties界面中选择压缩bit流(可选),并设置BITSTREAM.GENERAL.COMPRESS true [current_design]即可。

代码各式说明

1、CFGBVS参数:当CFGBVS连接至Bank 0的VCCO时,需确保Bank 0的VCCO为2.5V或3.3V,若使用Bank 14或15的I/O进行配置,也需确保这些Bank的VCCO为相应的电压值。

2、CONFIG_VOLTAGE:设置为对应的配置电压,此处为3.3V。

3、BITSTREAM.GENERAL.COMPRESS:用于压缩BIT文件。

4、BITSTREAM.CONFIG.CONFIGRATE等参数:仅适用于纯FPGA的配置,对于ZYNQ不支持。

本文详细介绍了在Xilinx FPGA的Vivado设计中如何设置bit文件的配置模式及相关的约束设置,合理地设置这些约束可以确保FPGA设计的成功实现并优化资源利用。

还没有评论,来说两句吧...