温馨提示:这篇文章已超过409天没有更新,请注意相关的内容是否还可用!

摘要:本篇文章介绍了使用Verilog HDLbits实现12小时计时器的功能。文章详细解释了如何使用Verilog语言编写一个具有时钟功能的计时器,该计时器能够显示小时和分钟,并且具有循环计时功能。通过HDLbits工具,读者可以更容易地理解并实现这一功能。整体内容简洁明了,适合初学者了解和学习Verilog语言在数字电路设计中的应用。

本设计是关于使用Verilog HDL语言开发一个具有时钟功能的12小时计时器,通过HDLbits工具进行开发,该计时器能够准确显示小时数并在每满12小时时重置为零,此设计适用于数字电路学习和实践的初学者。

背景介绍

在数字电路和Verilog HDL语言的学习过程中,计时器是一个重要的实践项目,本次设计旨在实现一个功能全面的12小时计时器,以满足初学者学习和实践的需求。

设计概述

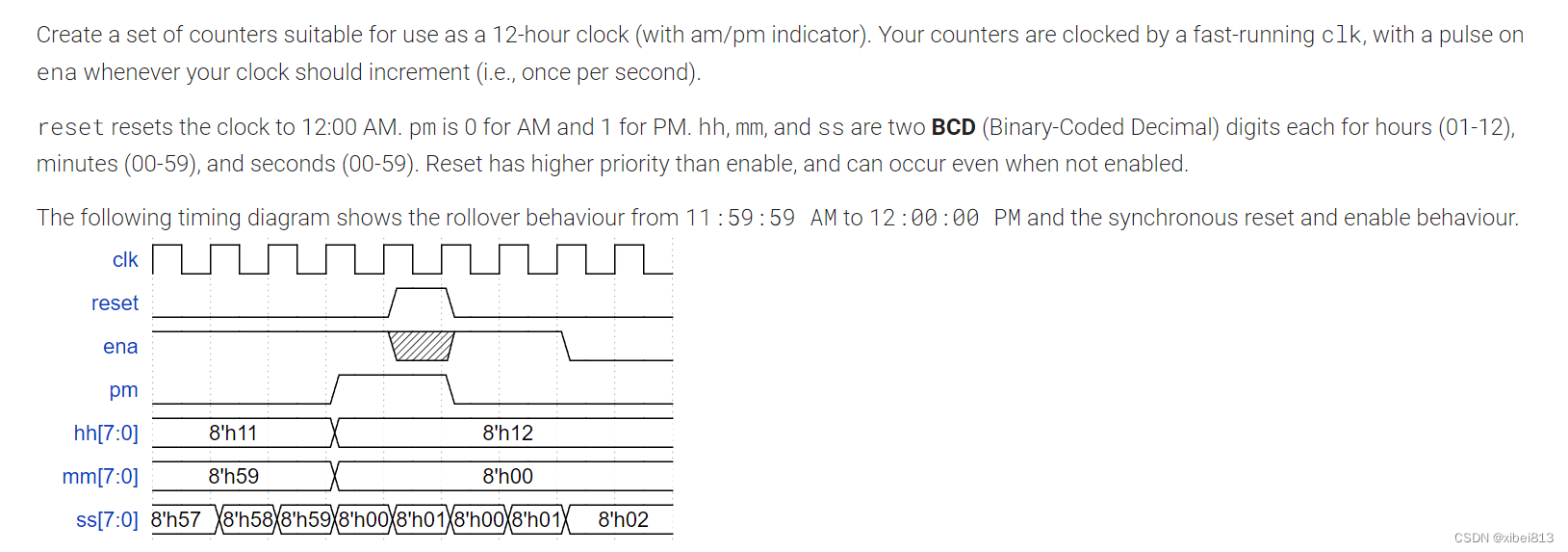

本设计的主要目标是创建一个适用于12小时制的计数器,该计数器由时钟信号clk驱动,每当clk信号的上升沿到来时,计数器就会根据ena信号进行更新,reset信号用于将计数器重置为初始状态,pm信号用于区分上午和下午,计时器的小时(hh)、分钟(mm)和秒(ss)采用BCD格式表示。

设计思路及实现

1、代码优化:对原始代码进行格式化和逻辑优化,确保代码的正确性和可读性。

2、时钟计数逻辑:基于clk信号进行时间累加,实现基本的计时功能。

3、重置逻辑:通过reset信号将计数器重置为凌晨12点的状态,同时处理pm信号以区分上午和下午。

4、BCD编码处理:确保小时、分钟和秒的输出采用BCD格式,便于显示和后续处理。

5、接口设计:确保计时器模块与其他模块之间的接口设计简洁、明确,以确保良好的模块间通信。

细节处理

在实现过程中,需要注意以下几点:

1、确保计时器的准确性,采取必要的措施避免计时误差。

2、处理好reset信号的触发时机和优先级问题,确保在任何情况下都能正确重置计数器。

3、处理好从上午11:59:59到下午12:00:00的转换问题,确保计时器能够平滑过渡。

4、严格遵守Verilog HDL语言的语法规则和编程习惯,确保代码的质量和可读性。

本设计成功实现了基于Verilog HDL语言的12小时计时器,为数字电路初学者提供了一个实践平台,该计时器具有基本的功能和良好的可读性,未来可以进一步优化设计,提高性能和功能,以满足更多应用场景的需求,可以添加闹钟功能、时间显示亮度调节等功能,以提升用户体验。

还没有评论,来说两句吧...