温馨提示:这篇文章已超过474天没有更新,请注意相关的内容是否还可用!

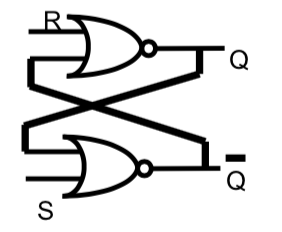

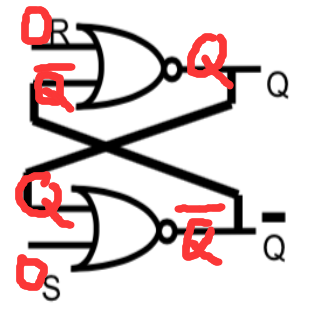

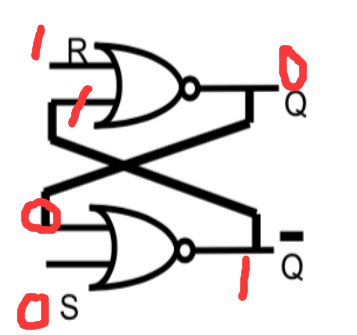

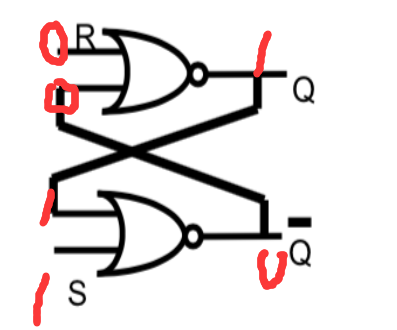

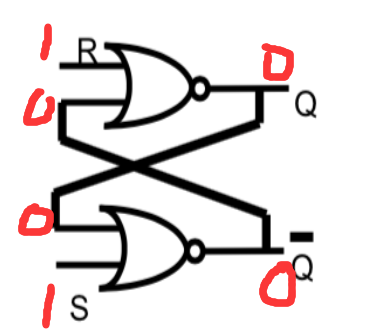

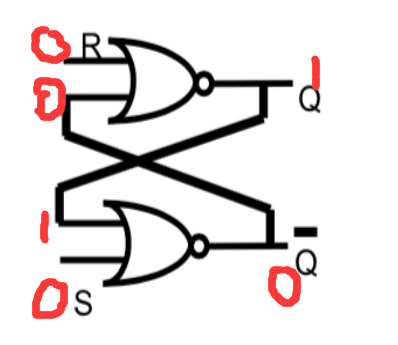

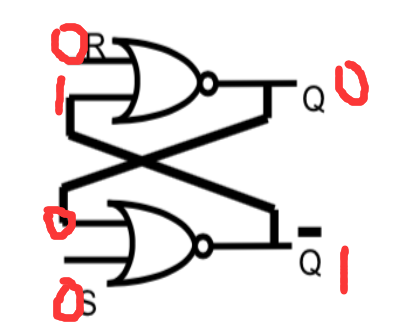

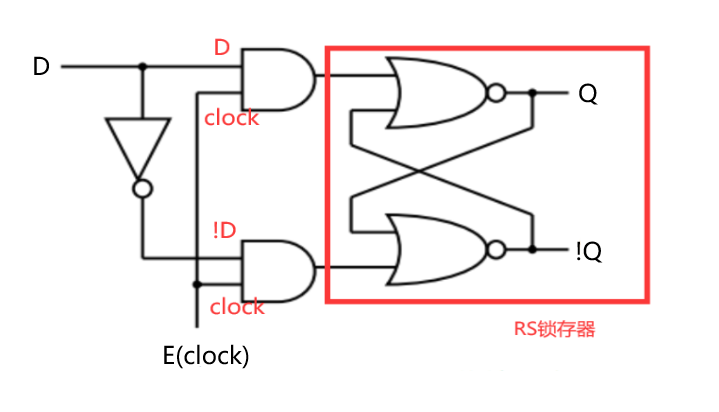

摘要:本文介绍了FPGA结构中的LATCH(锁存器)和FF(触发器)。LATCH是一种存储电路元件,具有使信号保持在其输出状态的能力,常用于数据路径中。而FF是一种时序逻辑电路,具有记忆功能,能够存储一个二进制值并在时钟信号触发时更新其状态。这两种元件在FPGA设计中扮演着关键角色,共同实现了数字系统的存储和时序控制功能。

清晰易懂:你的文章结构清晰,内容易于理解,每个部分都详细解释了FPGA中的相关概念,如LATCH、FF、触发器等,并用具体的图示和例子帮助读者理解。

2、丰富的实例:你使用了许多实例来解释概念,如D触发器的真值表、JK触发器的实现等,这些实例有助于读者更好地掌握知识点。

3、避免了冗余:你的文章避免了冗余的内容,每个部分都紧扣主题,不偏离核心知识点。

4、适当的互动性元素:你在文章中提出了一些问题,如“如何避免使用Verilog综合出LATCH”,这有助于引发读者的思考,增加互动性。

一些建议:

1、增加电路图解释:对于一些复杂的电路图,你可以增加一些解释或说明,以帮助读者更好地理解电路的工作原理。

2、深化实践应用:你可以增加一些实践应用方面的内容,如介绍一些实际项目中FPGA的应用案例,这将有助于读者更好地理解FPGA的实际价值。

3、拓展学习资源:在文章的最后,你可以提供一些拓展学习资源,如相关的教材、在线课程或网站,以帮助读者深入学习FPGA相关知识。

4、校对和修正:虽然你的文章内容已经很清晰,但建议在校对阶段再次检查,以确保没有遗漏或错误。

你的FPGA系列文章非常出色,内容详实、结构清晰、易于理解,希望以上建议能够帮助你进一步优化文章,使更多的读者受益。

文章版权声明:除非注明,否则均为VPS857原创文章,转载或复制请以超链接形式并注明出处。

还没有评论,来说两句吧...