温馨提示:这篇文章已超过462天没有更新,请注意相关的内容是否还可用!

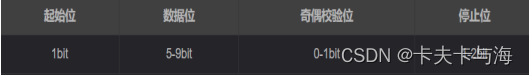

摘要:本文介绍了FPGA中UART串口通信的详细知识。UART作为一种常用的串行通信接口,在FPGA设计中扮演着重要角色。文章详细解释了UART串口通信的原理、工作流程以及关键参数设置,帮助读者深入理解FPGA UART串口通信的实现方式和优化方法。

程序代码(续)

② 串口发送模块(Verilog实现)

/*===================================*

文件名 : uart_tx.v

描述 : 串口发送模块

日期 : 2023年XX月XX日

作者 : XXX(你的名字)

*===================================*/

module uart_tx (

input wire clk, // 时钟信号,频率为50MHZ

input wire rst_n, // 复位信号,低电平复位

input wire tx_data, // 待发送数据

input wire tx_flag, // 数据使能标志位,高电平表示发送数据,低电平表示不发送数据

output reg uart_tx // UART串口发送数据线

);

// 系统时钟参数定义

parameter SCLK = 50_000_000; // 系统时钟频率为50MHZ

parameter BAUD_RATE = 115200; // UART通信波特率设置为115200bps

// 状态机定义

localparam IDLE = 2'b00, // 空闲状态

SEND = 2'b01; // 数据发送状态

reg [1:0] state_machine; // 状态寄存器,用于记录当前的状态机状态

reg [31:0] baud_rate_counter; // 波特率计数器,用于产生波特率延时效果,产生起始位和停止位以及数据位之间的间隔

reg [7:0] data_counter; // 数据位计数器,用于记录当前发送的数据位数量(包括起始位和停止位)

wire start_bit, stop_bit, data_bit; // 分别表示起始位、停止位和数据位信号输出

// TODO:实现状态机的转换逻辑,根据状态的变化控制数据的发送过程,当tx_flag为高电平时,开始发送数据,在SEND状态下,根据baud_rate_counter的值产生起始位、数据位和停止位的时序,当所有数据位发送完毕后,返回IDLE状态,同时需要处理异常情况,如数据溢出等,具体实现细节需要根据实际情况进行调整和优化,还需要添加必要的逻辑来处理数据的起始传输和结束传输时的特殊情况,确保数据的正确传输,验证部分还需要编写仿真测试代码,验证串口发送模块的正确性和性能,确保在实际应用中能够正确实现UART串口回环实验的功能,具体实现细节需要根据实际情况进行调整和完善,这里只是一个简单的示例代码框架,需要根据实际情况进行填充和完善。*/接下来是顶层模块和仿真验证部分的内容,这部分需要根据实际情况编写和完善,确保代码能够正确实现UART串口回环实验的功能,并通过仿真验证其正确性,对实验进行总结和归纳,以上代码仅为示例代码框架,需要根据实际情况进行填充和完善,特别是状态机的设计、波特率计数器的实现以及数据发送的具体逻辑需要详细设计和编写。

文章版权声明:除非注明,否则均为VPS857原创文章,转载或复制请以超链接形式并注明出处。

还没有评论,来说两句吧...