温馨提示:这篇文章已超过462天没有更新,请注意相关的内容是否还可用!

摘要:本文介绍了使用FPGA(现场可编程门阵列)和Verilog语言实现UART(通用异步收发器)传输协议来传输数据的流程。文章涵盖了从设计、编程到仿真的全过程。通过Verilog编写的UART模块,实现了数据的串行传输,并进行了仿真验证。本文为用户提供了一个利用FPGA实现UART数据传输的有效方法,包括仿真步骤,以确保设计的正确性和性能的优化。

目录

实现功能

1、接收UART串行数据,输出并行数据(1byte)。

2、输入并行数据(1byte),输出UART串行数据。

3、完成UART传输的1次环回。

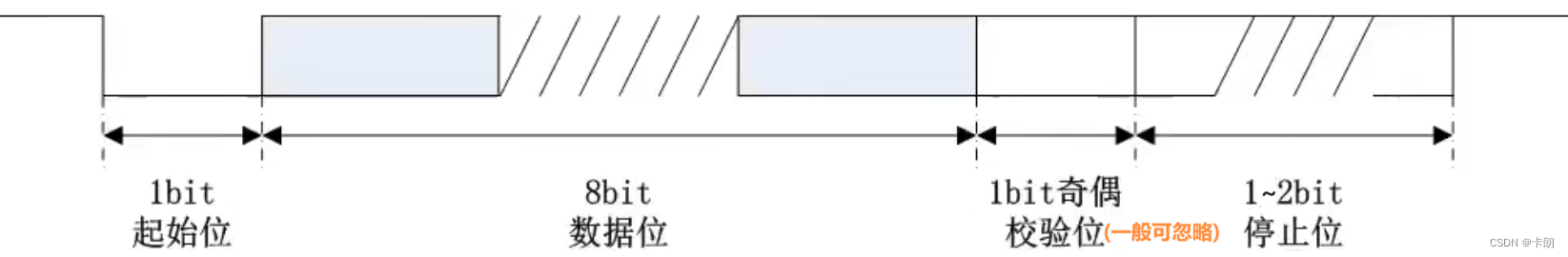

UART协议的1帧数据传输

对于UART通信,一帧数据通常包括起始位、数据位、可选的奇偶校验位和停止位,这里可以简要描述一下该模块如何处理这些位。

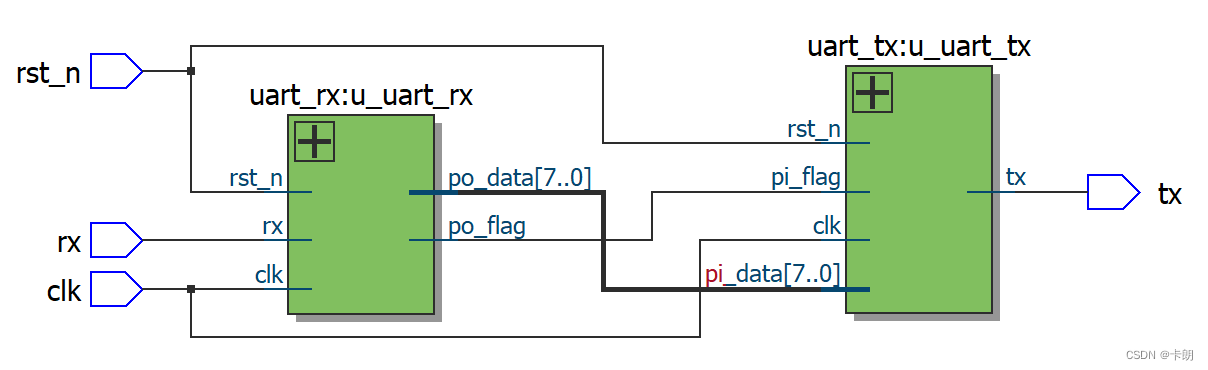

模块封装 - port设置

对于模块封装,需要清晰地定义每个端口的功能和参数。

clk: 时钟信号。

rst_n: 复位信号(低电平有效)。

rx: UART串行数据输入。

po_data: 并行数据输出(8位)。

po_flag: 有效并行数据的标志信号输出。

Verilog代码实现

uart接收模块: 接收串行数据, 输出并行数据和其有效标志

以下是一个简化的Verilog代码示例,用于实现UART接收模块的基本功能:

module uart_rx #(

parameter UART_BPS = 'd9600, // 波特率: 1s传输9600个bit

parameter CLK_FREQ = 'd50_000_000 // 时钟频率: 50MHz

) (

input wire clk, // 时钟信号输入

input wire rst_n, // 复位信号输入(低电平有效)

input wire rx, // UART串行数据输入

output reg [7:0] po_data, // 并行数据输出(8位)

output reg po_flag // 有效并行数据的标志信号输出

);

// ...(内部逻辑代码)...

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

// 复位逻辑代码...

end else begin

// 正常工作逻辑代码...

end

end内部逻辑代码需要根据具体的UART协议和硬件平台来实现,包括但不限于同步时钟、消除亚稳态、下降沿检测等,您提供的部分代码片段可以作为参考,但需要进一步完善和调试以确保正确工作,还需要编写发送模块、环回测试模块等,并整合到一个完整的系统中进行测试和验证。

还没有评论,来说两句吧...