温馨提示:这篇文章已超过449天没有更新,请注意相关的内容是否还可用!

摘要:本篇文章探讨了基于FPGA的数字信号处理中如何确定Verilog表达式的位宽。文章指出,确定Verilog表达式的位宽是设计数字信号处理系统的重要环节,涉及到信号特性、运算精度和硬件资源等多个因素。文章将介绍如何根据信号特性和处理需求,合理设定Verilog表达式的位宽,以实现高效的数字信号处理。

关于自决定表达式和上下文决定表达式

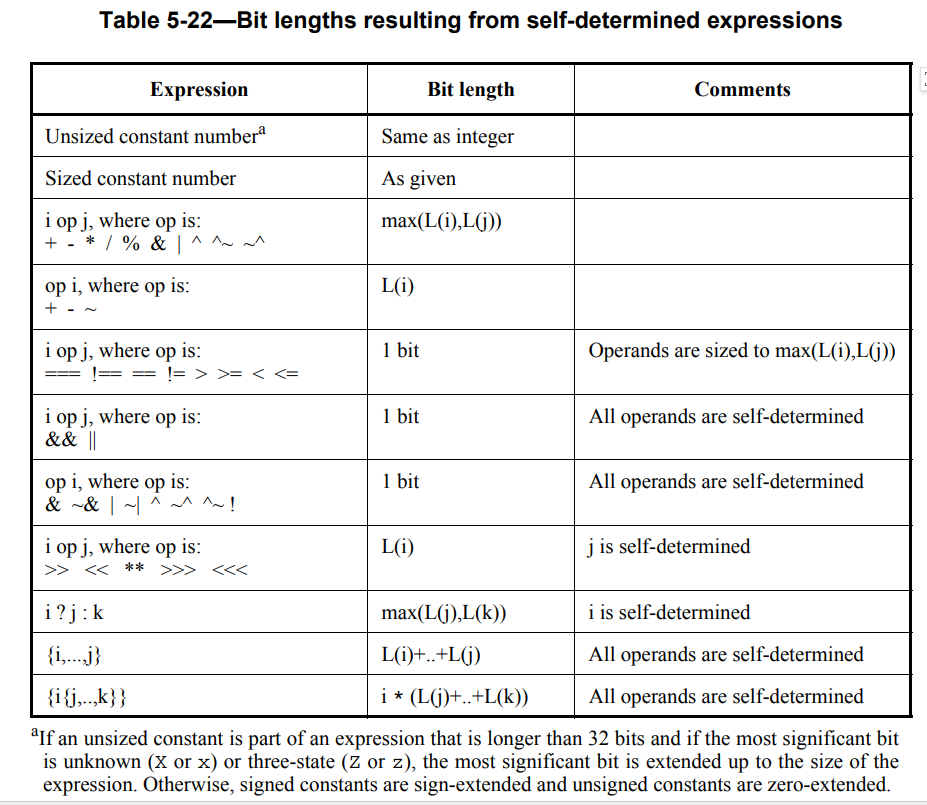

自决定表达式的位宽是根据表达式自身的特点和运算结果来确定的,而上下文决定表达式的位宽则是由整个表达式中最大的位宽来决定,理解这一点对于避免位宽相关的错误非常重要。

关于常数和变量的位宽

对于给定的位宽常数,其位宽就是给定的数值,而对于无位宽常数的表达式,其位宽通常默认为32位(在大多数编译器中),了解这一点有助于正确处理常数在表达式中的位宽问题。

关于运算表达式的位宽

在进行运算时,表达式的位宽往往取决于操作数的位宽,当两个不同位宽的数进行加减乘除等运算时,结果的位宽通常等于两个操作数中较大的那个,对于逻辑与、逻辑或等表达式,结果的位宽只有1位,理解这一点可以避免在复杂运算中出现位宽错误。

关于规约运算的位宽

规约运算是对数据本身的所有位进行同样的运算,因此结果的位宽只有1位,了解这一点有助于正确处理规约运算的位宽问题。

为了更好地理解和应用这些规则,建议在实际编程过程中多加练习,并注意观察和总结,也可以参考Verilog的官方文档和相关教程,以获取更详细和准确的信息。

我还想补充一点关于Verilog编程风格的建议,在编写Verilog代码时,尽量保持代码清晰、简洁和易于理解,使用有意义的变量名、合理的注释和格式化输出等良好的编程习惯,有助于提高代码的可读性和可维护性,这对于减少错误、提高开发效率以及团队合作都非常重要。

文章版权声明:除非注明,否则均为VPS857原创文章,转载或复制请以超链接形式并注明出处。

还没有评论,来说两句吧...